# Science & Technology Policy Brief Semiconductor Chip Manufacturing

Semiconductors or chips power modern electronics and require highly advanced manufacturing processes. This brief outlines the background and technological challenges associated with semiconductor manufacturing.

# Background

Semiconductor chips are building blocks of electronic technology.<sup>1</sup> Cars, laptops, smartphones, virtual reality and industrial robots, all rely on chips. The chip industry is a USD 500 billion business that is expected to grow to 1.3 trillion by 2029.<sup>2,3</sup> It is an R&D focussed industry and the global supply chain is highly specialised and concentrated in a few regions. India does not have any high-volume production chip manufacturing facilities (or fabs). The total consumption of electronic chips in India was worth around Rs 1.1 lakh crore in 2020, all of which was met through imports.<sup>4</sup> The central government has announced schemes amounting to Rs 76,000 crore to create fabs in India. This brief outlines various technological challenges associated with chip manufacturing.

*Semiconductors* are materials which have electrical properties different from conductors (such as copper, aluminium, silver) and insulators (glass, ceramics, plastic). They conduct electricity only under certain conditions. This means that they can be used as switches (ON/OFF) by changing the underlying conditions. A *transistor* is a device made up of a semiconductor that controls electric voltage and current by acting as an ON/OFF switch. This property is utilised to represent states, for instance, OFF as 0 and ON as 1. As all information can be represented as a combination of 0s and 1s (binary system), transistors become fundamental to computing in digital devices.<sup>5</sup>

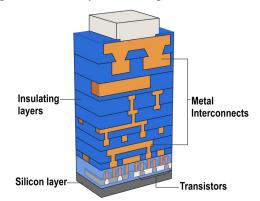

Modern chips contain millions (and even billions) of transistors and other electronic components in complex three-dimensional circuits (see Figure 1).<sup>6</sup>

## Summary

- A chip contains millions of electronic switches (transistors) on a flat silicon piece.

- Manufacturing chips involves use of light to print tiny circuits on silicon wafer.

- Three major challenges in manufacturing chips are achieving high resolution, ensuring accuracy and mass production.

- Global supply chain is highly specialised (design, equipment, materials, fabrication) and concentrated in a few places.

- Governments across the world have initiated schemes for domestic chip production facilities.

The smaller the transistor, the more of these can be packed into the same area. Smaller chips use less electrical energy and generate less heat. Technological advances have helped pack more transistors per chip, doubling every two years, resulting in more computing power. For example, the iPhone 12 (2020) is about a billion times faster than the Apollo 11 guidance computer used in the 1969 US space mission.<sup>7,8</sup> Such compact packing is possible due to reduction in transistor's dimensions to the order of nanometres (nm) which is a billionth of a metre (10<sup>-9</sup> m). It means a nanotransistor is roughly 50,000-1,00,000 times smaller than the width of a human hair.<sup>9</sup>

The advancement in chip-industry is characterised by process or technology *node numbers*, e.g., 180nm, 130-nm, and 65-nm. The smaller the node number, the denser the circuitry that results in better performance of the device. <sup>10,11,12,13</sup> For example, advanced smartphones today use 7-nm technology. It means that there are around 10 crore transistors per square mm.<sup>10</sup>

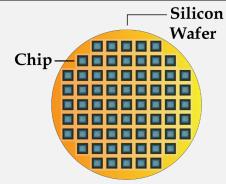

The commonly used semiconductor material is silicon (Si) which is the second most abundant element in earth's crust. Thin circular slices of silicon (called wafers) are used in chip production.

#### Box 1: Chip node number as per application<sup>14,15,16,17,18</sup>

| Chips needed for     | Node           |

|----------------------|----------------|

| Cars                 | 180 nm - 40 nm |

| Home appliances      | 130 nm – 90 nm |

| Laptops, Smartphones | Below 15 nm    |

**Fabrication process:** Chips are made up of interconnected complex patterns of transistors created layer by layer on pure silicon wafers (about

| Mayank Shreshtha    |  |

|---------------------|--|

| mayank@prsindia.org |  |

300 mm diameter). The manufacturing of chip involves multiple elements and steps.<sup>19</sup>

*Design:* Chips are made up of multiple layers (up to 100) such that patterns are overlayed on top of the previous layer with nanometre precision.<sup>20</sup> Special design software are used to draw a blueprint of 3D architecture of these layers.<sup>21</sup>

*Photomask:* The blueprint of the designed pattern is then transferred onto an opaque plate with transparent areas, called a 'mask'.<sup>22</sup> The mask is generally four times larger than the intended pattern on the chip.<sup>23</sup> Light passing through this plate imprints the miniaturised version of the pattern on the chip.

*Lithography:* Lithography or Photolithography is a projection system, i.e., it puts the image of the circuit on to the silicon surface. A silicon wafer is first deposited with layer of silicon or other materials. A thin coating of light-sensitive material is applied on the wafer. Next, the light is projected through the mask and the lens shrinks it and focusses the encoded pattern onto tiny regions of light-sensitive wafer. The exposed patterns are left to bake and develop. Unexposed areas on the photosensitive coating are removed to engrave the pattern onto the surface.

Electrically-charged atoms (ions) are showered on the exposed etched patterns to create transistors. Other materials such as copper wires and silicon dioxide (an insulator) are deposited to connect the transistors in a circuit. The light-sensitive layer is then removed. The lithography and the above process is repeated, and layers with different patterns are created. Finally, layers are stacked up and cut into tiny parts, resulting into a chip.

#### Figure 1: Inner layers of a chip

*Fabrication cleanrooms*: Given the small resolution, even a nanoscale particle or virus can potentially damage the pattern on the wafer, and render it useless. A cleanroom (with stable temperature and humidity levels) is required which typically contains 1,000 times fewer dust particles than a sterile operation theatre.<sup>24</sup>

Assembly and testing of chips: Fabrication firms generally make a pizza-sized (~300 mm) wafer printed with many chips. The wafer needs to be cut

into actual chips and then encased with a protective layer of ceramic or plastic for easier handling. These 'assembly' or 'packaging' steps are generally done by other companies. A final testing needs to be done to ensure quality. Then, a chip is ready to be plugged in smartphones or laptops.

## **Technological Challenges**

For successful commercial deployment, lithography technologies need to satisfy three criteria: resolution, accuracy and productivity. A machine with higher resolution can make increasingly smaller patterns. A more accurate machine will imprint them without any errors. For mass production, companies need to produce the wafers at a rapid pace. Each of these criteria face several technological challenges.

#### **Challenge 1: Achieving High Resolution**

Lithography uses light to expose the patterns on the silicon wafer. The thickness of the patterns cannot be less than the wavelength of light hitting the wafer. Therefore, instead of visible light (wavelength 400-700 nm), deep ultraviolet (DUV) light (wavelength 193 nm) is used.<sup>25</sup>

The amount of light that can be collected and focussed using lenses and mirrors also matters.<sup>26</sup> 193 nm-DUV lithography machines have brought down the resolution to 63 nm from 2,000 nm.<sup>27,28</sup> To go below 63 nm and print even finer details, chipmakers project light through a layer of ultrapure water (or other imaging fluids) between the lens and the silicon wafer.<sup>29</sup> The water increases the amount of light collected and results in improved resolution. Thus, it acts an additional lens. This technique is called DUV *immersion lithography*. A few examples of DUV-made chips are 90, 65 and 45 nm nodes.

However, 193 nm is still larger than the size of patterns that modern chips need. The most advanced chips now use extreme ultraviolet (EUV) light which has about 14 times shorter wavelength than DUV (13.5 nm).<sup>30</sup> EUV effectively acts as a sharper pencil while carving patterns on chips than DUV light. EUV enables the drawing of features up to 10-15 nm. <sup>31,32</sup>

EUV light occurs naturally only in outer space and gets absorbed by air and lenses. Artificial production of EUV light is an extremely difficult task and requires powerful lasers and a sophisticated setup. Special extremely-smooth multi-layered mirrors are required to collect and focus on the wafer during the fabrication.<sup>33</sup> The whole process happens in a vacuum chamber. Globally, ASML in the Netherlands is the only company that makes high-end EUV machines.<sup>25</sup> The latest models of advanced smartphones use EUV-made chips.<sup>34,35</sup> EUV machines are currently only being used by a few top chip manufacturing companies.

**Combined DUV and EUV:** Since a chip contains many layers stacked on top of each other, the more intricate layers can be printed using EUV and the others with DUV.<sup>23,36</sup> This is done to ensure cost-effectiveness during the chip-making process.

## **Challenge 2: Ensuring Accuracy**

**Pattern defects:** While EUV light has improved the resolution of lithography systems, making accurate patterns without errors remains a challenge. Currently, EUVs result in random defects on the circuit in the form of imperfectly made holes, line breaks or bridges between two lines.<sup>37</sup> Next-generation EUV machines will need to address this challenge.

**Measurement errors:** The small wavelength of EUV (13.5 nm) creates problems in measuring the accuracy of the etched patterns.<sup>38</sup> Further reduction in dimensions can impact the quality of accuracy and precision measurement of the patterns.

#### Semiconductor Production Chain: Company Types<sup>20</sup>

**Integrated Device Manufacturers (IDMs):** Some companies such as Intel (US) and Samsung Electronics (South Korea) both design and manufacture chips.

**Fabrication Companies (Fabs):** Fabs manufacture chips under contract for other companies, e.g., Taiwan Semiconductor Manufacturing Company (TSMC), UMC and GlobalFoundries. In 2021, TSMC (54%), Samsung (17%) and GlobalFoundries (7%) constituted about 80% of all manufactured chips.<sup>39</sup> TSMC accounts for more than 90% of advanced chips (below 10 nm nodes).<sup>40</sup>

Fabless Companies: These companies research and design chips but send their production to fabs, e.g. US-based NVIDIA, AMD, and Qualcomm, and MediaTek (Taiwan).

Lithography equipment manufacturers: ASML (Netherlands) and Japan-based Nikon and Canon. In 2020, sales share of all lithography machines (DUVs and EUVs) were: ASML (91%), Nikon (6%) and Canon (3%).<sup>41</sup> Only ASML makes EUV machines used for making advanced chips.

Japan leads the market in speciality chemicals and silicon ingots which are crucial for semiconductor manufacturing.  $^{\rm 42}$

## **Challenge 3: Mass Production**

**Wafer tables and precision printing:** The lithography machine first scans and prints on a small portion of the loaded wafer and then moves to the next portion. These steps need to be achieved at a high speed with minimum vibration. Magnetically levitating wafer tables are used in the process.<sup>43,44</sup> Before a pattern is exposed onto a silicon wafer, it must be precisely scanned. While one wafer is being exposed, simultaneously another wafer table measures the positioning of wafer. This is done 20,000 times per second using the machine's sensors with an accuracy of 0.06 nm.

**Clean rooms:** The area of a typical cleanroom depends on the yield of fabrication plant or fab, i.e.,

number of wafers produced per month. While the clean room of a mini-fab (~10k wafers per month) is around 30,000 square metres, that of a mega-fab (~25k wafers per month) is 1,00,000 square metres, and of a gigafab (more than 1 lakh wafer per month) is about 1,60,000 square metres.<sup>45,46,47,48</sup> Expensive heating, ventilation and air-conditioning systems are required to maintain the necessary purity levels in such vast spaces.

**High purity water:** Presence of even a nano-sized particle (chemical impurities, bacteria or virus) in the water used for immersion lithography can sabotage the intricate design on the wafer.<sup>49,50</sup> Also, since the set up is moving at high-speed, water bubbles should not form; otherwise, the resolution of the equipment will be affected. Therefore, dissolved gases are removed from water before it is put into the system.

During lithography, various unwanted particles, chemicals and metal debris (from construction of connections between transistors) are left. A sequential wet cleaning using ultrapure water is needed to rinse off the contamination. Also, more layers in a chip increase the amount of water needed.

**Waste water treatment:** More than 400 chemical products are typically used in a chip production plant.<sup>51</sup> The waste water left over from the wet cleaning steps contains high amounts of chemicals. Exposure to these chemicals can potentially cause health problems. Hence, proper water treatment is critical.<sup>51,52</sup> Big fabrication companies such as TSMC (Taiwan) recycle about 87% of the waste water whereas the industry average is 42%.<sup>53,54</sup>

#### Timeline of technological milestones

1947/1948: First Transistor<sup>55</sup>

1959: Integrated circuit (IC) or Chip<sup>56</sup>

1970: First commercial memory chip (DRAM)<sup>57</sup>

1971: First commercial microprocessor/CPU (10 micrometre (μm or 10<sup>-6</sup> m) nodes, ~2300 transistors)<sup>58</sup>

2001: Intel Pentium 4 chip (180 nm, ~42 million transistors)<sup>58</sup>

2004/2005: DUV immersion Lithography<sup>25,59</sup>, 65-nm process node

2019: First commercial EUV-made 7-nm chip<sup>60,61</sup>

2022: Apple M1 Ultra (~114 billion transistors) chip<sup>62</sup>

**Size and Cost of Lithography Machines:** The smaller the patterns on the chip, the bigger the lithography machine needed, as a larger set of lens or mirrors are required and more energy-intensive equipment is needed. The current EUV machines are the size of a school bus and contain one lakh moving parts.<sup>63</sup> The cost of a basic EUV machine is about USD 150 million.<sup>64</sup> The next generation EUV machine is even bigger than the basic version and costs about USD 300 million.<sup>65</sup>

In contrast, DUV immersion systems are smaller and cost around 60 million euros. The price of dry systems (without water or imaging fluids between lens and wafer) averages around 20 million euros.<sup>66</sup>

## **Looking Ahead**

**Next-generation EUV machines:** It took almost 30 years to build an EUV light source with 13.5 nm. The next-generation EUV machines rely on increasing the amount of light which the mirrors can collect. These systems with larger mirrors are expected to enter the market by 2025 or 2026. They would reduce the minimum feasible resolution on the circuit from 13 nm to 8 nm.<sup>31, 67</sup>

**Increasing performance:** As the resolution size starts hitting limits, other methods for increasing computing power will have to be used.<sup>38</sup> These will involve stacking transistors on top of each other, tweaking with their structure, and improving the interconnects between transistors.

**Quantum effects:** The smallest transistors usually suffer from quantum effects, e.g., getting unwanted leakage current even when transistor is in off state.<sup>38</sup> These effects will become more pronounced as pattern gets smaller and smaller. Such effects can interfere and disrupt the operation of the chip.

**Power and cooling problem:** As the dimensions of transistors are reduced, it becomes difficult to bring power into the chip.<sup>38</sup> Extracting heat from the chip is also a problem. Improved and efficient power delivery and cooling mechanisms are needed to advance further.

## **Indian Semiconductor Scenario**

At present, India does not have any commercial fab, and all chip requirement is met through imports. However, various multinationals as well as Indian IC design service providers have large design houses in India.<sup>42,68</sup> Once the designs are completed, they are sent for fabrication to United States, South Korea or Taiwan.

**R&D in Semiconductors in India:** The Center of Excellence in Nanoelectronics launched in 2006 have developed R&D expertise in India. Ministry of Electronics and Information Technology (MeitY) Special Manpower Development Program (SMDP) has enabled IC design R&D and talent development.<sup>69,70</sup> Semi-Conductor Lab (SCL) Mohali's 180nm CMOS line has been leveraged by strategic agencies like ISRO, DRDO, and academic institutions to develop design and technology IP as well as talent development. To address the lack of domestic chip manufacturing capabilities, India has initiated different programs that are listed below.

**Semicon India Program:** With a total outlay of Rs 76,000 crore (~ USD 10 billion), India has approved three major schemes to address the issues related to semiconductor industry.<sup>71</sup>

(i) *Semiconductor fabs*: Fiscal support of 50% of the total project cost will be provided for construction of two new fabrication facilities.<sup>72</sup>

(ii) Other chip-related fabs and assembly and testing facilities: Fiscal support of 50% for setting up compound semiconductors/ light-based silicon semiconductors/sensors fabs. Compound semiconductors refer to chips made up of two elements, e.g., Gallium Nitride (GaN) as opposed to pure silicon. Similar support is also given for the construction of assembly, testing, marking and packaging (ATMP) facilities and Outsourced Semiconductor Assembly and Test (OSAT) companies.<sup>73</sup>

#### Government Support in US and EU:

**US CHIPS Act:** The Creating Helpful Incentives to Produce Semiconductors and Science (CHIPS) Act of 2022, allocated around USD 280 billion to boost semiconductor capacity, accelerate innovation and create a bigger STEM workforce over a period of 10 years.<sup>74</sup> About USD 200 billion is given for R&D and commercialisation followed by constructing domestic chip manufacturing facilities (~USD 53 billion).

**EU Chips Act:** The Act aims to increase to the chip production in EU from less than 10% to 20% of total world production. EU has mobilised about USD 46 billion of public and private investment until 2030 to attain the manufacturing goal.<sup>75</sup>

(iii) *Design-Linked Scheme:* This scheme provides financial incentives and infrastructure support for development of electronic design components such as IC, chipsets and new chip architectures over a period of five years.

The program also includes the construction of display (e.g., LCD screens) fabs and modernisation of SCL Mohali. India Semiconductor Mission (ISM) is the nodal agency for the implementation of schemes for the development of chips and manufacturing ecosystem in India.

Scheme for Promotion of Manufacturing of Electronic Components and Semiconductors (SPECS): MeitY has an additional scheme which provides financial incentive of 25% on capital expenditure for domestic manufacturing of electronic components, construction of semiconductors fab units and ATMP units.<sup>76</sup> <sup>1</sup> Miller, C. (2022). *Chip War: The Fight for the World's Most Critical Technology*. Simon and Schuster.

<sup>2</sup> Press Release, Gartner, January 19, 2022,

https://www.gartner.com/en/newsroom/press-releases/2022-01-19-gartner-says-worldwide-semiconductor-revenue-grew-25point-one-percent-in-2021-exceeding-500-billion-for-the-firsttime.

<sup>3</sup> 'The global semiconductor market is projected to grow from \$573.44 billion in 2022 to \$1,380.79 billion by 2029, at a CAGR of 12.2% in forecast period, 2022-2029', Fortune Business Insights, April 2022,

https://www.fortunebusinessinsights.com/semiconductormarket-102365.

<sup>4</sup> Unstarred Question No. 505, Lok Sabha, Ministry of Electronics and Information Technology, July 20, 2022, https://pqals.nic.in/annex/179/AU505.pdf.

<sup>5</sup> Shannon, C. E. (1948). A mathematical theory of communication. *The Bell system technical journal*, *27*(3), 379-423.

https://pure.mpg.de/rest/items/item\_2383162\_7/component/file\_2456978/content.

<sup>6</sup> 'The basics of microchips', ASML (as accessed on March 22, 2023), <u>https://www.asml.com/en/technology/all-about-microchips/microchip-basics</u>.

<sup>7</sup> 'Fast-forward — comparing a 1980s supercomputer to the modern smartphone', Adobe blog, (as accessed on March 22, 2023), https://blog.adobe.com/en/publish/2022/11/08/fast-forward-comparing-1980s-supercomputer-to-modern-smartphone.

<sup>8</sup> 'Your phone is now more powerful than your PC', Samsung, August 19, 2021,

https://insights.samsung.com/2021/08/19/your-phone-is-now-more-powerful-than-your-pc-3/.

<sup>9</sup> 'How small is nanoscale small?', Australian Academy of Science (as accessed on March 22, 2023)

https://www.science.org.au/curious/technology-future/howsmall-nanoscale-small.

<sup>10</sup> Moore, S. K. (2020). A better way to measure progress in semiconductors, *IEEE Spectrum*, <u>https://spectrum.ieee.org/abetter-way-to-measure-progress-in-semiconductors</u>.

<sup>11</sup> H.-S. P. Wong *et al.*, "A Density Metric for Semiconductor Technology [Point of View]," in *Proceedings of the IEEE*, vol. 108, no. 4, pp. 478-482, April 2020,

https://ieeexplore.ieee.org/document/9063714

<sup>12</sup> Courtland, R. (2017). Intel now packs 100 million transistors in each square millimeter. *IEEE Spectrum*, *30*, https://spectrum.ieee.org/intel-now-packs-100-milliontransistors-in-each-square-millimeter.

<sup>13</sup> 'Let's Clear Up the Node Naming Mess', Intel Newsroom, March 29, 2017, <u>https://newsroom.intel.de/news-releases/letsclear-node-naming-mess/.</u>

<sup>14</sup> 'Analog chips – poised to become the next big threat to automakers?', S&P Global Mobility, January 27, 2022, https://www.spglobal.com/mobility/en/research-analysis/analogchips-poised-to-become-the-next-big-threat-to-automakers.html.

<sup>15</sup> STM32 Microcontrollers, Wikipedia (as accessed on March 22, 2023), <u>https://en.wikipedia.org/wiki/STM32</u>.

<sup>16</sup> Core i5 – Intel, WikiChip (as accessed on March 23, 2023), https://en.wikichip.org/wiki/intel/core\_i5.

<sup>17</sup> Snapdragon 662 - Qualcomm, WikiChip (as accessed on March 23, 2023),

https://en.wikichip.org/wiki/qualcomm/snapdragon\_600/662. <sup>18</sup> 'AMD "Zen" Core Architecture', AMD (as accessed on

March 24, 2023), <u>https://www.amd.com/en/technologies/zen-</u> core.

<sup>19</sup> '6 crucial steps in semiconductor manufacturing', ASML, October 6, 2021,

https://www.asml.com/en/news/stories/2021/semiconductormanufacturing-process-steps.

<sup>20</sup> 'How microchips are made', ASML (as accessed on March 22, 2023), https://www.asml.com/en/technology/all-aboutmicrochips/how-microchips-are-made. <sup>21</sup> Electronic Design Automation, Wikipedia (as accessed on March 22, 2023),

https://en.wikipedia.org/wiki/Electronic\_design\_automation. <sup>22</sup> 'Printing circuits onto wafers: 'Photoresist'', Samsung,

January 6, 2021,

https://semiconductor.samsung.com/support/toolsresources/dictionary/photoresist-printing-the-circuit-onto-thewafer/.

<sup>23</sup> 'Our Technology', ASML (as accessed on March 22, 2023), https://www.asml.com/en/technology.

<sup>24</sup> Factsheet, Intel, October 25, 2007,

https://www.intel.com/pressroom/kits/manufacturing/Fab32/AZ Factsheet\_FNL.pdf.

<sup>25</sup> 'Light and lasers', ASML (as accessed on March 22, 2023), https://www.asml.com/en/technology/lithographyprinciples/light-and-lasers.

<sup>26</sup> 'The Rayleigh criterion', ASML (as accessed on March 22, 2023), <u>https://www.asml.com/en/technology/lithography-principles/rayleigh-criterion</u>.

<sup>27</sup> Lin, B. J. (2006). Optical lithography—present and future challenges. *Comptes Rendus Physique*, 7(8), 858-874, https://www.sciencedirect.com/science/article/pii/S1631070506 002179/pdf?md5=8b43b144163864fcb71a3c924673f11b&pid=1-s2.0-S1631070506002179-main.pdf.

<sup>28</sup> Based on Rayleigh Criterion, Critical Dimension or Resolution = Process factor ( $k_1$ ) × wavelength/Numerical Apertutre (N.A).  $k_1$  quantifies all the other effects and physical limits of the lithography machine. N.A is the amount of light the optics system can collect and focus. For DUV (wavelength = 193 nm,  $k_1$  = 0.3, N.A. = 0.93), hence resolution is about 63 nm.

<sup>29</sup> Bruce W. Smith, Yongfa Fan, Michael Slocum, Lena Zavyalova, "25 nm immersion lithography at 193 nm wavelength," Proc. SPIE 5754, Optical Microlithography XVIII, (12 May 2005); https://doi.org/10.1117/12.602414.

<sup>30</sup> 'EUV lithography systems', ASML (as accessed on March 22, 2023), <u>https://www.asml.com/en/products/euv-lithography-systems</u>.

<sup>31</sup> Based on Rayleigh Criterion,  $k_1 = 0.25$ , EUV wavelength is 13.5 nm and N.A of current EUV system = 0.33. Next-generation High N.A EUV = 0.55). Hence, 10 nm to 6 nm theoretical shrinkage is predicted.

<sup>32</sup> 'EUV Lithography: A European Joint Project', Zeiss, October 20, 2021, <u>https://www.zeiss.com/semiconductor-manufacturing-technology/smt-magazine/euv-lithography-as-an-european-joint-project.html</u>.

<sup>33</sup> 'Lenses and mirrors', ASML (as accessed on March 22, 2023), https://www.asml.com/en/technology/lithography-principles/lenses-and-mirrors.

<sup>34</sup> A14 Bionic – Apple, WikiChip (as accessed on March 22, 2023), <u>https://en.wikichip.org/wiki/apple/ax/a14</u>.

<sup>35</sup> 'Samsung Introduces the Industry's First 5nm Processor Powering the Next Generation of Wearables ', Samsung, August 2021,

https://semiconductor.samsung.com/newsroom/news/samsungintroduces-the-industrys-first-5nm-processor-powering-the-nextgeneration-of-wearables/.

<sup>36</sup> 'DUV lithography systems', ASML (as accessed on March 22, 2023), <u>https://www.asml.com/en/products/duv-lithographysystems</u>.

<sup>37</sup> 'Sailing along the stochastic cliffs', imec, June 28, 2019, https://www.imec-int.com/en/imec-magazine/imec-magazinejuly-2019/euv-lithography-sailing-along-the-stochastic-cliffs.

<sup>38</sup> 'Smaller, better, faster: imec presents chip scaling roadmap', imec, February 2, 2023, <u>https://www.imec-</u>

int.com/en/articles/smaller-better-faster-imec-presents-chipscaling-roadmap.

<sup>39</sup> '2 charts show how much the world depends on Taiwan for semiconductors', CNBC, March 15, 2021,

https://www.cnbc.com/2021/03/16/2-charts-show-how-muchthe-world-depends-on-taiwan-for-semiconductors.html

<sup>40</sup> 'TSMC: how a Taiwanese chipmaker became a linchpin of the

global economy', Financial Times, March 24, 2021, https://www.ft.com/content/05206915-fd73-4a3a-92a5-6760ce965bd9.

<sup>41</sup> If You Invested \$10,000 in ASML in 2010, This Is How Much You Would Have Today', NASDAQ, February 3, 2022, https://www.nasdaq.com/articles/if-you-invested-%2410000-inasml-in-2010-this-is-how-much-you-would-have-today.

<sup>42</sup> Page 39, Strengthening the global semiconductor value chain in uncertain era, Semiconductor Industry Association and BCG, April 2021, <u>https://www.semiconductors.org/wp-</u> context/unloade/0021/05/BCC v. SIA\_Strengthening the Clobal

content/uploads/2021/05/BCG-x-SIA-Strengthening-the-Global-Semiconductor-Value-Chain-April-2021\_1.pdf.

<sup>43</sup> 'Mechanics and mechatronics', ASML (as accessed on March 22, 2023), https://www.asml.com/en/technology/lithographyprinciples/mechanics-and-mechatronics.

<sup>44</sup> Yoon, D. (2019). Design and Optimal Control of a Magnet Assisted Scanning Stage for Precise and Energy Efficient Positioning (Doctoral dissertation),

https://deepblue.lib.umich.edu/bitstream/handle/2027.42/149847 /yydkyoon\_1.pdf?sequence=1&isAllowed=y.

<sup>45</sup> GIGAFAB Facilities, TSMC (as accessed on March 29, 2023),

https://www.tsmc.com/english/dedicatedFoundry/manufacturing /gigafab.

<sup>46</sup> 'TSMC Completes Construction of 5nm Fab 21 in Arizona', Tom's Hardware, July 29, 2022,

https://www.tomshardware.com/news/tsmc-fab-21-arizona. <sup>47</sup> Figure 1, TSMC F14P3 Fab building information, An

optimized LEED's green fab at TSMC,

https://www.irbnet.de/daten/iconda/CIB\_DC25553.pdf.

<sup>48</sup> 'TSMC starts to build fab 18: 5 nm, Volume production in Early 2020', AnandTech, January 31, 2018,

https://www.anandtech.com/show/12377/tsmc-starts-to-build-fab-18-5nm-in-early-2020.

<sup>49</sup> 'Purity on another level - 'Ultra pure water'', Samsung, May 22, 2020, https://semiconductor.samsung.com/support/toolsresources/dictionary/purity-on-another-level-ultrapure-water/. <sup>50</sup> https://www.mks.com/n/semiconductor-ultrapure-water

<sup>51</sup> Kim, S., *et al.* (2018). Chemical use in the semiconductor manufacturing industry. *International journal of occupational and environmental health*, 24(3-4), 109–118. https://doi.org/10.1080/10773525.2018.1519957.

<sup>52</sup> Yoon, C. (2012). Much concern but little research on semiconductor occupational health issues. *Journal of Korean Medical Science*, *27*(5), 461-464,

https://www.ncbi.nlm.nih.gov/pmc/articles/PMC3342533/pdf/jkms-27-461.pdf.

<sup>53</sup> 'Water Management', TSMC (as accessed on March 22, 2023),

https://esg.tsmc.com/en/focus/greenManufacturing/waterResour ceManagement.html.

<sup>54</sup> Best Practice Guide in Water Efficiency, wafer fabrication and semiconductor sector – version 1, Public Utilities Board, Singapore, July 2018,

https://www.pub.gov.sg/Documents/Water\_Efficiency\_Wafer\_F abrication\_and\_Semiconductor\_Sector.pdf.

<sup>55</sup> '1956 Nobel Prize in Physics', Nokia Bell Labs (as accessed on March 22, 2023), <u>https://www.bell-</u>

labs.com/about/awards/1956-nobel-prize-physics/. <sup>56</sup> The chip that changed the world', Texas Instruments,

September 15, 2020, <u>https://news.ti.com/blog/2020/09/15/the-chip-that-changed-world</u>.

<sup>57</sup> Memory lane. *Nature Electronics*, 1, 323 (2018), https://doi.org/10.1038/s41928-018-0098-9.

<sup>58</sup> Intel Chips timeline, Intel,

https://www.intel.in/content/dam/www/public/us/en/documents/ corporate-information/history-intel-chips-timeline-poster.pdf. <sup>59</sup> 'TWINSCAN: 20 years of lithography innovation', ASML (as accessed on March 22, 2023),

https://www.asml.com/en/news/stories/2021/twinscan-20-years-innovation.

<sup>60</sup> 'Making EUV: from lab to fab', ASML, March 30, 2022, https://www.asml.com/en/news/stories/2022/making-euv-lab-tofab.

<sup>61</sup> 'Samsung Exynos 9825', Nanoreview.net (as accessed on March 22, 2023), <u>https://nanoreview.net/en/soc/samsungexynos-9825</u>.

<sup>62</sup> 'Apple unveils M1 Ultra, the world's most powerful chip for a personal computer', Apple, March 8, 2022,

https://www.apple.com/in/newsroom/2022/03/apple-unveilsm1-ultra-the-worlds-most-powerful-chip-for-a-personalcomputer/.

<sup>63</sup> 'EUV: The Most Precise, Complex Machine at Intel', Intel, December 21, 2021,

https://www.intel.com/content/www/us/en/newsroom/news/euvmost-precise-complex-machine.html.

<sup>64</sup> 'The \$150 Million Machine Keeping Moore's Law Alive', August 30, 2021, <u>https://www.wired.com/story/asml-extreme-ultraviolet-lithography-chips-moores-law/</u>.

<sup>65</sup> 'ASML sales boom continues as Intel places high-NA order', Optics.org, January 19, 2022, <u>https://optics.org/news/13/1/28</u>.

<sup>66</sup> 'We underestimated the demand for DUV', Bits&Chips, February 4, 2021, <u>https://bits-chips.nl/artikel/we-underestimated-the-demand-for-duv/</u>.

<sup>67</sup> 'The \$150 Million Machine Keeping Moore's Law Alive', August 30, 2021, <u>https://www.wired.com/story/asml-extreme-ultraviolet-lithography-chips-moores-law/</u>.

<sup>68</sup> 'Increased importance of VLSI design ecosystem in India for worldwide semiconductor Industry', Mahindra Tech (as accessed on March 29, 2023),

https://www.techmahindra.com/en-in/blog/increased-importance-of-vlsi-design-ecosystem/.

<sup>69</sup> Ganguly, U., Lashkare, S., & Ganguly, S. (2020). India's Rise in Nanoelectronics Research. *arXiv preprint*,

https://arxiv.org/abs/2011.11251.

<sup>70</sup> Microelectronics Development Division, Ministry of Electronics and Information Technology website (as accessed on March 29, 2023),

https://www.meity.gov.in/content/microelectronicsdevelopment-division.

<sup>71</sup> 'Indian Semiconductor Mission', Press Information Bureau, Ministry of Electronics and Information Technology, February 3, 2023,

https://pib.gov.in/PressReleasePage.aspx?PRID=1896018.

<sup>72</sup> Modified Scheme for setting up of Semiconductor Fabs in India, Ministry of Electronics and Information Technology, October 4, 2022,

https://www.meity.gov.in/writereaddata/files/Notification%20M odified%20Scheme%20for%20Semiconductor%20Fabs.pdf.

<sup>73</sup> F. W-38/21/2022-IPHW, Ministry of Electronics and Information Technology, October 4, 2022,

https://www.meity.gov.in/writereaddata/files/Notification%20M odified%20Scheme%20for%20Compound%20Semiconductor% 20ATMP.pdf.

<sup>74</sup> 'The CHIPS and Science Act: Here's what's in it', Mckinsey & Company, October 4, 2022,

https://www.mckinsey.com/industries/public-and-social-

sector/our-insights/the-chips-and-science-act-heres-whats-in-it. <sup>75</sup> European Chips Act, European Commission, February 2022,

https://ec.europa.eu/newsroom/dae/redirection/document/83080. <sup>76</sup> Notification W-18/30/2019-IPHW, Ministry of Electronics and Information Technology, April 1, 2020,

https://www.meity.gov.in/writereaddata/files/scheme\_for\_prom\_ otion\_of\_manufacturing\_of\_electronic\_components\_and\_semic onductors.pdf.

DISCLAIMER: This document is being furnished to you for your information. You may choose to reproduce or redistribute this report for non-commercial purposes in part or in full to any other person with due acknowledgement of PRS Legislative Research ("PRS"). The opinions expressed herein are entirely those of the author(s). PRS makes every effort to use reliable and comprehensive information, but PRS does not represent that the contents of the report are accurate or complete. PRS is an independent, not-for-profit group. This document has been prepared without regard to the objectives or opinions of those who may receive it.